I2C(Inter-Intergrated Circuit)总线是微电子通信控制领域中常用的一种总线标准,具有接线少,控制方式简单,通信速率高等优点。

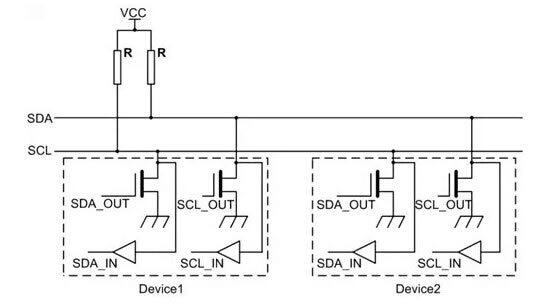

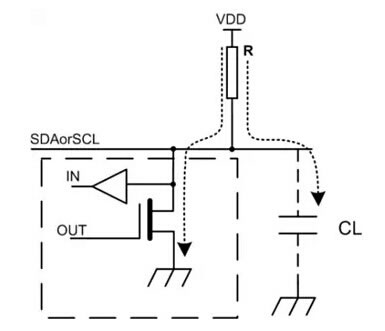

I2C总线的内部结构图如图1所示,I2C器件连接到总线输出级必须是集电极开路或漏极开路形式才能实现线“与”的逻辑功能。输出端未接上拉电阻的时候只能输出低电平,所示保证I2C总线正常工作输出端必须接上拉电阻。

在I2C电路中常见的上拉电阻是1K,1.5K,2.2K,3.3K,4.7K,5.1K,10K等等,但选哪一个阻值更合适?

图1 I2C总线内部结构

I2C总线上拉电阻阻值如何选?

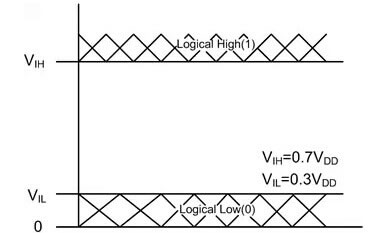

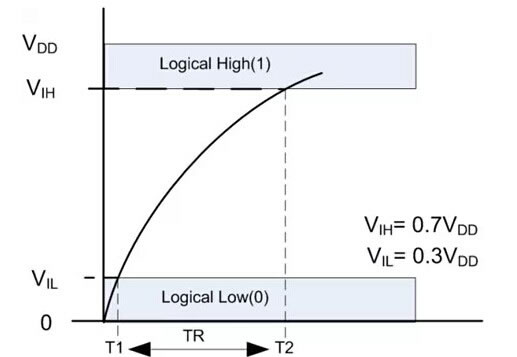

I2C规范将低于VIL或低于0.3VDD的电压定义为逻辑低电平,同样将高于VIH或高于0.7VDD的电压定义为逻辑高电平,如图2所示。

图2 指定为逻辑高电平和逻辑低电平的电压电平

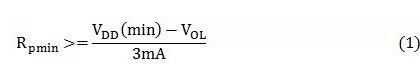

电源电压限制了可允许总线拉低的最小上拉电阻值,过强的上拉会阻止器件充分拉低拉线的电平,导致无法确保逻辑低电平能被检测到。在输出级V_OLmax=0.4V 时指定I_OL为3mA,允许总线电压拉低的最小上拉电阻公式:

V_DD与Rp的函数关系分别如图3所示。

图3 Rp的最小值是电压的函数

由于端口的输出的高电平是通过上拉电阻实现,线上的电平从低变到高时,电源通过上拉电阻对线上负载电容CL充电,这需要一定的时间,即上升时间,上拉电阻的最大值由总线容限负载决定,总线负载图如图4所示。

图4 总线负载结构图

总线电容主要由引脚、连接、PCB走线和导线等因素引起,总线电容与上拉电阻R具有一个RC时间常数,随着I2C通信速率的增加,该常数变得越发重要。通过电阻对电容进行充电的一般公式:

重新排列,

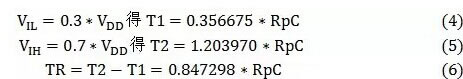

之后我们可计算电压上升至VIL的时间T1、上升至VHL的时间T2以及精确计算两个电平之间的时间TR,如图5所示。由于VIL与VHL都是有V_DD产生,因此该公式与电源电压无关,V_DD项已抵消。

图5 总线电平上升时间

求解,

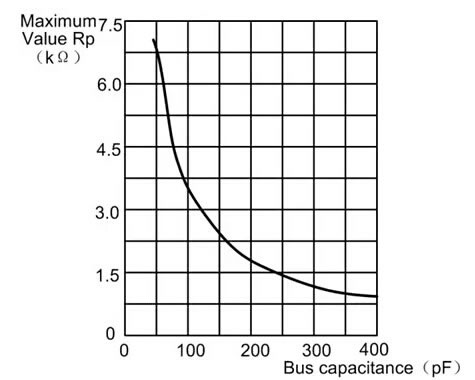

在I2C标准模式下,100Kbps总线的负载最大容限小于等于400pF;快速模式,400Kbps总线的负载最大容限小于等于200pF,快速模式下I2C总线上升时间更快,总线上拉电阻要比标准模式小,设计时以快速模式50Pf~200pF为参考,由上面(6)式得最大Rp值与总线电容的关系如图6所示。

图6 符合快速模式I2C总线TRmax要求的Rp最大值是总线电容的函数

由上面的计算可得出上拉电阻RP可以取的范围是1.53K~7K @VDD = 5V,一般取5.1K ,综合到3.3V VDD低功耗设计中,通常选用4.7K牺牲速度换取电池使用时间,此阻值也是常规阻值。

关于I2C的上拉电阻,最好的方式是看官方给出的参考设计,如果走线长了或总线上有多从机,就相应把电阻改小一些,如若参考设计没有就在计算范围内选用一个常规阻值。实际的时候我们没有去测量总线电容的问题,只能在选件、走线的时候给予些许关注。

文章转载自:致远电子