毫无疑问,布线是整个PCB设计中最重要、最费时的工序,直接影响着 PCB 板的性能好坏。作为一名合格的、优秀的PCB设计工程师,除了要把线布通外,更要满足其电气性能、让线整齐美观,而这需要工程师掌握一些布线技巧。

走线长度

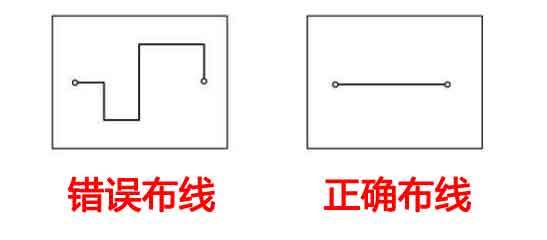

1. 使走线长度尽可能的短

在 PCB 布线时,应该使走线长度尽可能的短,以减少由走线长度带来的干扰问题。

2. 调整走线长度

数字电路系统对时序有严格的要求,为了满足信号时序的要求,对PCB上的信号走线长度进行调整已经成为PCB设计工作的一部分。

走线长度的调整包括以下两个方面的要求:

a. 要求走线长度保持一致,保证信号同步到达若干个接收器。有时在PCB上的一组信号线之间存在着相关性,如总线,就需要对其长度进行校正,因为需要信号在接收端同步。调整方法就是找出其中最长的那根走线,然后将其他走线调整到等长。

b. 控制两个器件之间的走线延迟为某一个特定值,如控制器件A、B之间的导线延迟为1ns,而这样的要求往往由电路设计者提出,但由PCB工程师去实现。需要注意的是,在PCB上的信号传播速度是与PCB的材料、走线的结构、走线的宽度、过孔等因素相关的。通过信号传播速度,可以计算出所要求的走线延迟对应的走线长度。

走线长度的调整常采用的是蛇形线的方式。

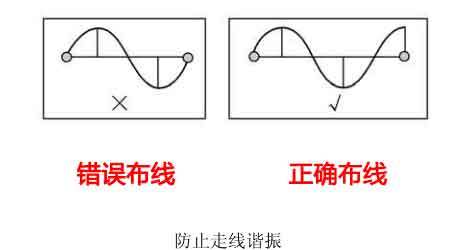

3、防止走线谐振

在PCB布线时,布线长度不得与其波长成整数倍关系,以免产生谐振现象。

超实用PCB布线技巧,菜鸟和老司机都应该知道

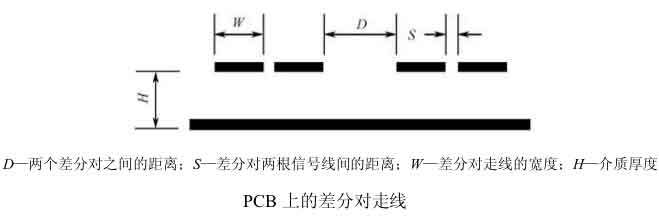

差分对走线

为了避免不理想返回路径的影响,可以采用差分对走线。为了获得较好的信号完整性,可以选用差分对走线来实现高速信号传输。

1. 差分信号传输优点:

a. 输出驱动总的di/dt会大幅降低,从而减小了轨道塌陷和潜在的电磁干扰。

b. 与单端放大器相比,接收器中的差分放大器有更高的增益。

c. 差分信号在一对紧耦合差分对中传输时,在返回路径中对付串扰和突变的鲁棒性更好。

d. 因为每个信号都有自己的返回路径,所以差分信号通过接插件或封装时,不易受到开关噪声的干扰。

2. 差分信号的缺点:

a. 如果不对差分信号进行恰当的平衡或滤波,或者存在任何共模信号,就可能会产生EMI问题。

b. 与单端信号相比,传输差分信号需要双倍的信号线。

3. 设计差分对走线时,要遵循以下原则:

a. 保持差分对的两信号走线之间的距离S在整个走线上为常数。

b. 确保D>2S,以最小化两个差分对信号之间的串扰。

c. 使差分对的两信号走线之间的距离S满足S=3H,以便使元件的反射阻抗最小化。

d. 将两差分信号线的长度保持相等,以消除信号的相位差。

e. 避免在差分对上使用多个过孔,因为过孔会产生阻抗不匹配和电感。

电源、地线的处理

即使在整个PCB板中的布线完成的很好,但由于电源和地线的考虑不周到而引起的干扰,会使产品的性能下降,有时甚至会影响到产品的成功率。所以对电源和地线的处理要认真对待,把电源和地线的所产生的噪音和干扰降到最低限度,以保证产品的质量。

1)尽量加宽电源和地线的宽度,最好是地线比电源线宽,它们的关系是:地线—电源线—信号线。

2)对数字电路的PCB可用宽的地导线组成一个回路,即构成一个地网来使用(模拟电路的地不能这样使用)

3)用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。或是多层板,电源和地线各占用一层。

数字电路与模拟电路的共地处理

现在许多PCB不再是单一功能电路,而是由数字电路和模拟电路混合构成的。因此在布线时就需要考虑它们之间互相干扰的问题,特别是地线上的噪音干扰。

数字电路的频率高,模拟电路的敏感度强,对信号线来说,高频的信号线尽可能远离敏感的模拟电路器件,对地线来说,整个PCB对外界只有一个结点,所以必须在PCB内部进行处理数字和模拟共地的问题,而在板内部数字地和模拟地实际上是分开的,它们之间是互不相连的,只是在PCB与外界连接的接口处(如插头等)。数字地与模拟地有一点短接,(请注意,只有一个连接点),也有在PCB上不共地的,这由系统设定来决定。

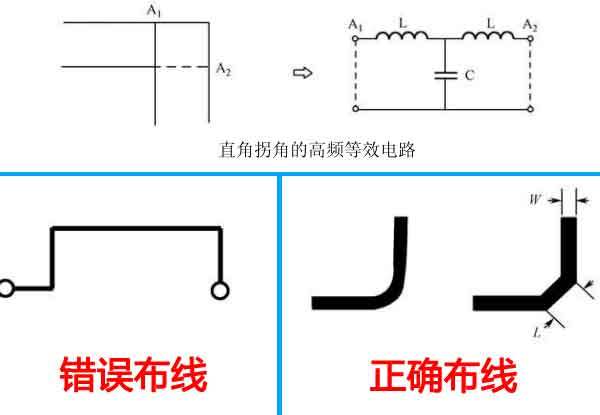

拐角设计

在PCB布线时,走线拐弯是不可避免的,当走线出现直角拐角时,在拐角处会产生额外的寄生电容和寄生电感。走线拐弯的拐角应避免设计成锐角和直角形式,以免产生不必要的辐射,同时锐角和直角形式的工艺性能也不好。要求所有线与线的夹角应大于等于135°。在走线确实需要直角拐角的情况下,可以采取两种改进方法:一种是将90°拐角变成两个45°拐角;另一种是采用圆角。圆角方式是最好的,45°拐角可以用到10GHz频率上。对于45°拐角走线,拐角长度最好满足L≥3W。

控制PCB导线的阻抗和走线终端匹配

在高速数字电路PCB和射频电路PCB中,对PCB导线的阻抗是有要求的,需要控制PCB导线的阻抗。在PCB布线时,同一网络的线宽应保持一致。由于线宽的变化会造成线路特性阻抗的不均匀,对高速数字电路传输的信号会产生反射,故在设计中应该尽量避免出现这种情况。在某些条件下,如接插件引出线、BGA封装的引出线等类似的结构时,如果无法避免线宽的变化,应该尽量控制和减少中间不一致部分的有效长度。

在高速数字电路中,当PCB布线的延迟时间大于信号上升时间(或下降时间)的1/4时,该布线即可以看成传输线。为了保证信号的输入和输出阻抗与传输线的阻抗正确匹配,可以采用多种形式的终端匹配方法,所选择的匹配方法与网络的连接方式和布线的拓扑结构有关。

免责声明:本文为网络转载文章,转载此文目的在于传播相关技术知识,版权归原作者所有,如涉及侵权,请联系小编删除(联系邮箱:service@eetrend.com )。