本文的关键要点

・具备驱动器源极引脚,可以大大降低导通损耗和关断损耗。

・如果ID导通峰值或VDS关断浪涌因开关速度提升而增加,就需要采取对策。

在上一篇文章中,我们通过工作原理和公式了解了有无驱动器源极引脚的差异和效果。有驱动器源极引脚的MOSFET可以消除源极引脚的电感带来的影响,从而可降低开关损耗。在本文中,我们将通过双脉冲测试来确认驱动器源极引脚的效果。

驱动器源极引脚的效果:双脉冲测试比较

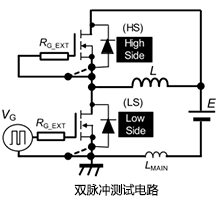

为了比较没有驱动器源极引脚的MOSFET和有驱动源极引脚的MOSFET的实际开关工作情况,我们按照右图所示的电路图进行了双脉冲测试,在测试中,使低边(LS)的MOSFET执行开关动作。

高边(HS)MOSFET则通过RG_EXT连接栅极引脚和源极引脚或驱动器源极引脚,并且仅用于体二极管的换流工作。在电路图中,实线是连接到源极引脚的示意图,虚线是连接到驱动器源极引脚的示意图。

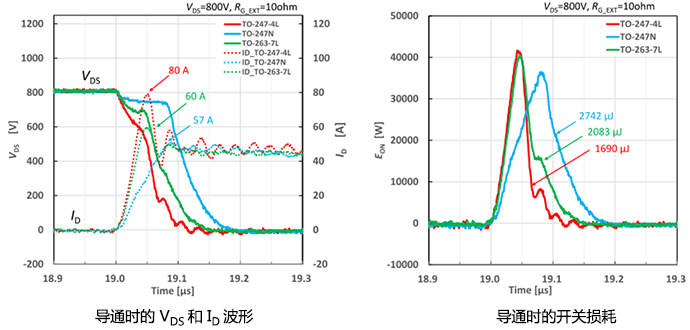

我们来分别比较导通时和关断时的漏-源电压VDS和漏极电流ID的波形以及开关损耗。测试中使用的是最大额定值(VDSS的波形以及开关损耗。测试中使用的是最大额定值(RDS(on))为 40mΩ的SiC MOSFET。TO-247N封装的产品(型号:SCT3040KL)没有驱动器源极引脚,TO-247-4L(SCT3040KR)和TO-263-7L(SCT3040KW7)有驱动器源极引脚。这是在RG_EXT为10Ω、施加电压VHVDC为800V、ID为50A左右的驱动条件下的波形。

与没有驱动器源极引脚的TO-247N封装产品(浅蓝色虚线)相比,有驱动器源极引脚的TO-247-4L封装产品(红色虚线)和TO-263-7L封装产品(绿色虚线)导通时的ID上升速度更快。通过比较,可以看出TO-247N封装产品(浅蓝色线)的开关损耗为 2742µJ,而TO-247-4L封装产品(红色线)为1690µJ,开关损耗减少约38%;TO-263-7L封装产品(绿线)为 2083µJ,开关损耗减少24%,减幅显著。

通过导通波形可以确认,TO-247-4L的ID峰值达到了80A,比TO-247N大23A。这是因为,尽管在MOSFET的开关工作过程中对COSS的充放电能量是恒定的,但由于驱动器源极引脚可提高开关速度,所以充放电时间缩短,最终导致充电电流的峰值变大。虽然HS侧MOSFET的误启动也会导致峰值电流增加,但这不是误启动造成的。

TO-263-7L的ID峰值为60A,不如TO-247-4L的大。这是由于换流侧MOSFET(HS)的封装电感不同造成的,与后续会介绍的关断浪涌的差异成因一样。也就是说,由dID/dt产生的开关侧(LS)和换流侧MOSFET的总封装电感引起的电动势,会将开关侧MOSFET的VDS压低,并使开关侧MOSFET的COSS中积蓄的能量被释放,但TO-263-7L的放电电流很小,导通时的ID峰值也很小。

此外,导通时的开关损耗EON也是由于相同的原因,TO-247-4L封装产品的开关侧MOSFET的VDS被压低,最终使开关损耗EON降低。

但是,如果TO-247-4L和TO-263-7L没有采取误启动对策,发生误启动时导通电流的峰值可能会进一步增加,因此建议务必采取误启动对策,比如在米勒钳位电路或栅极-源极之间连接几nF的电容。如果希望进一步了解详细信息,请参考应用指南中的“SiC-MOSFET 栅极-源极电压的浪涌抑制方法”。

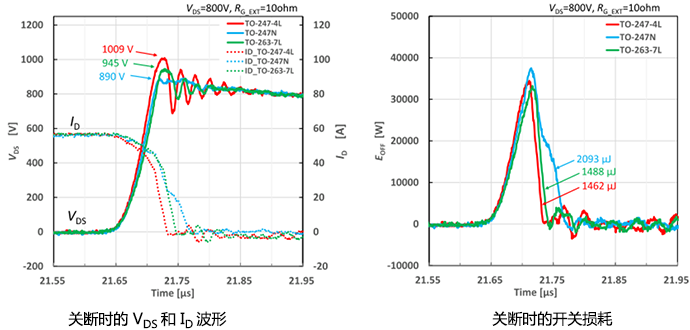

接下来是关断时的波形。可以看出,TO-247N封装产品(浅蓝色实线)的开关损耗为2093µJ,TO-247-4L封装产品(红色实线)为1462µJ,开关损耗降低约30%,TO-263-7L封装产品(绿色实线)为1488µJ,开关损耗降低约29%,即使降幅没有导通时那么大,也已经是很大的改善。

关断时在VDS中观测到的关断浪涌的主要起因是主电路的总寄生电感。它是前面给出的双脉冲测试电路中的布线电感LMAIN与开关侧和换流侧MOSFET的封装电感(LDRAIN+LSOURCE)的合计值。因此,对于封装电感几乎相同的TO-247-4L(红色实线)和TO-247N(浅蓝色实线)而言,浪涌会随着dID/dt速度的升高而增加。在该测试中,TO-247-4L为1009V,比TO-247N的890V大119V,因此可能需要采取缓冲电路等浪涌对策。

同为带有驱动器源极引脚的产品,TO-263-7L(绿色实线)的浪涌比TO-247-4L(红色实线)小,是因为封装结构不同。TO-263-7L的漏极被分配到封装背面的散热片,并被直接焊接在PCB上。另外,由于源极引脚被分配给7个引脚中的5个引脚,因此封装电感小于TO-247-4L。请注意,开关侧的浪涌会随着换流侧(而非开关侧)封装电感的减小而变小。

关于开关损耗的比较信息汇总如下:

文章来源:罗姆半导体集团