问:时钟噪声对于高速DAC相位噪声的影响

时钟相位噪声的产生

时钟决定何时发送下一样本,故相位(或时序)中的任何噪声都会直接影响输出的相位噪声。

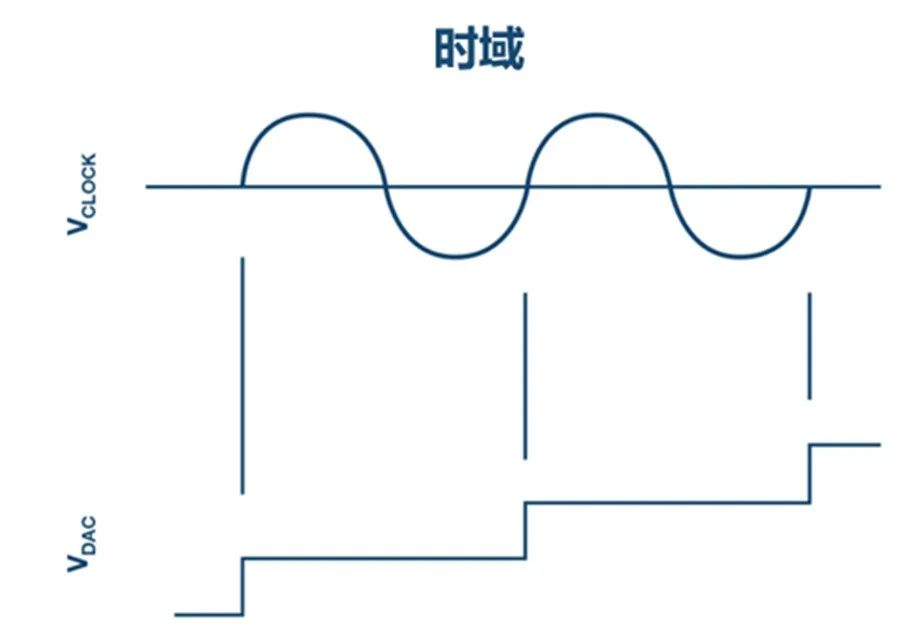

图 1:时钟与相位噪声的相关性

如上图所示,时钟对相位噪声的影响,可以视作各相继离散值与一个矩形函数相乘,其时序由时钟定义。

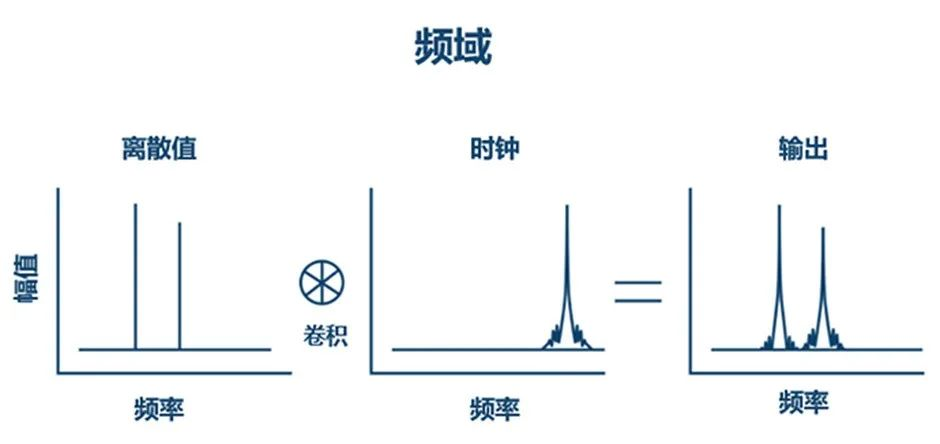

图 2:相位噪声卷积

如上图所示,在频域中,乘法转换为卷积运算。结果,期望的频谱被时钟相位噪声所破坏。这就是整个时钟相位噪声的产生的过程。

信号频率与相位噪声

根据信号频率与时钟频率之比,相对于载波的噪声放大或缩小。信号频率每降低一半,噪声改进6dB。为了证明这一点,下图是不同频率(5GHz,1GHz,500MHz)下,混入一个带有轻度100kHz相位偏移的调制时钟信号(精密受控),来模拟相位噪声,来看看信号频率与相位噪声的关系。

图 3 :带100kHz相位调制的时钟输出相位噪声 (图片来源:ADI)

我们可以看到,从5GHz时钟到500 MHz DAC输出观测到20dB降幅,从500MHz输出到1GHz输出观测到6dB增幅。

时钟噪声对于DAC相位噪声的影响很大。选择一个高精度的晶振可能是最简单的方案。

文章来源:得捷电子DigiKey