在当今的封装设计行业中,设计重用是加快设计周期的关键,因为上市速度决定了产品能否大获成功。大多数的封装设计都可能采用引线键合,因此可以在不同的设计中共享引线键合信息非常重要。然而,设计重用和 ECO(Engineering Change Order,工程变更命令)可能会造成与引线键合相关的封装设计问题,从而影响设计完整性,有时还会在设计过程的后期阶段导致设计失败。

Cadence Allegro Package Designer Plus 工具集提供了强大的检查功能,可以发现设计中的此类问题,并尽可能自动解决这些问题。本文将详细探讨这些针对引线键合的设计完整性检查。

运行具体引线键合相关的封装设计完整性检查

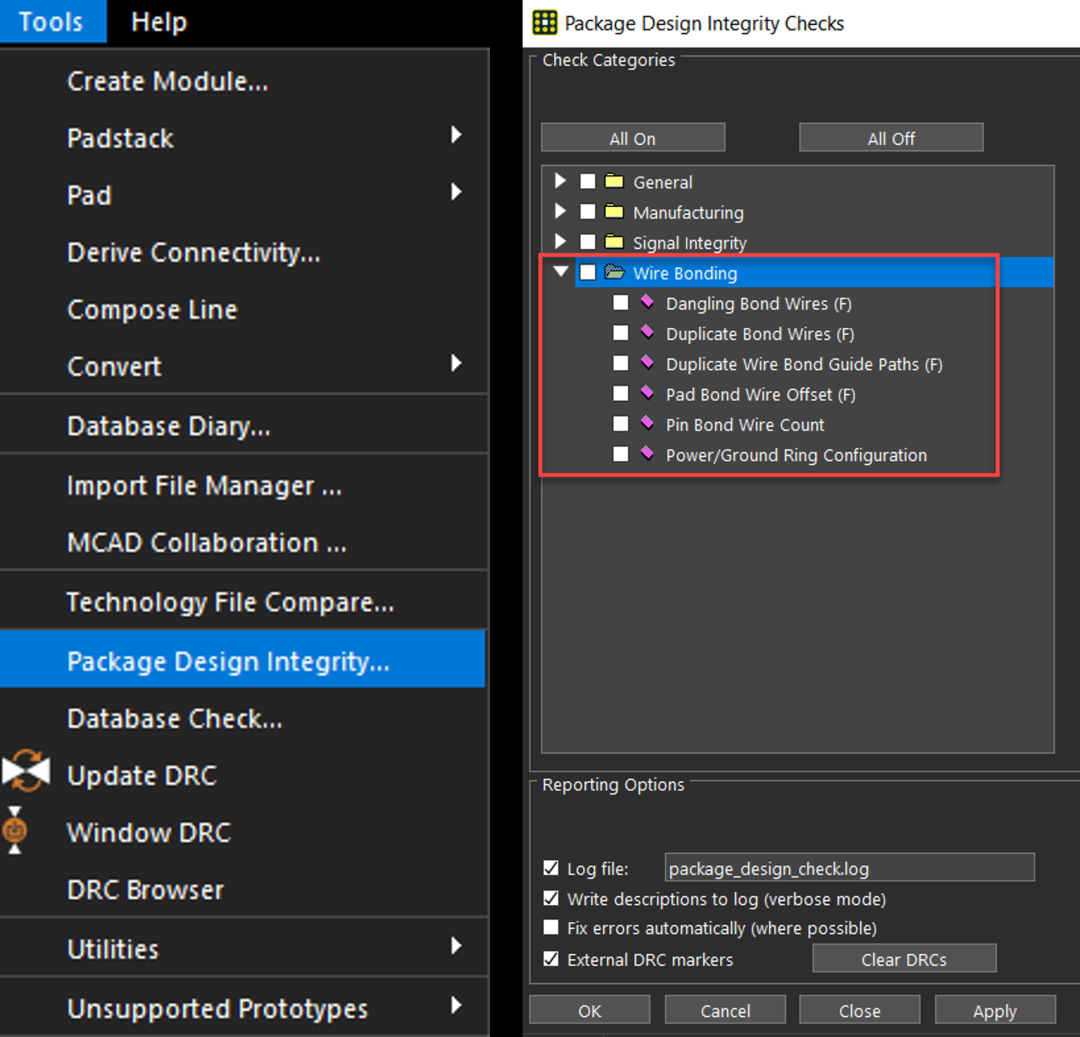

在 Allegro Package Designer Plus 中运行封装设计完整性检查的方法如下:

1. 选择 Tools ─ Package Design Integrity

打开 Package Design Integrity Checks 对话框。 2. 选择 Wire Bonding 检查并点击 Apply 此类别下的所有检查都针对引线键合运行。

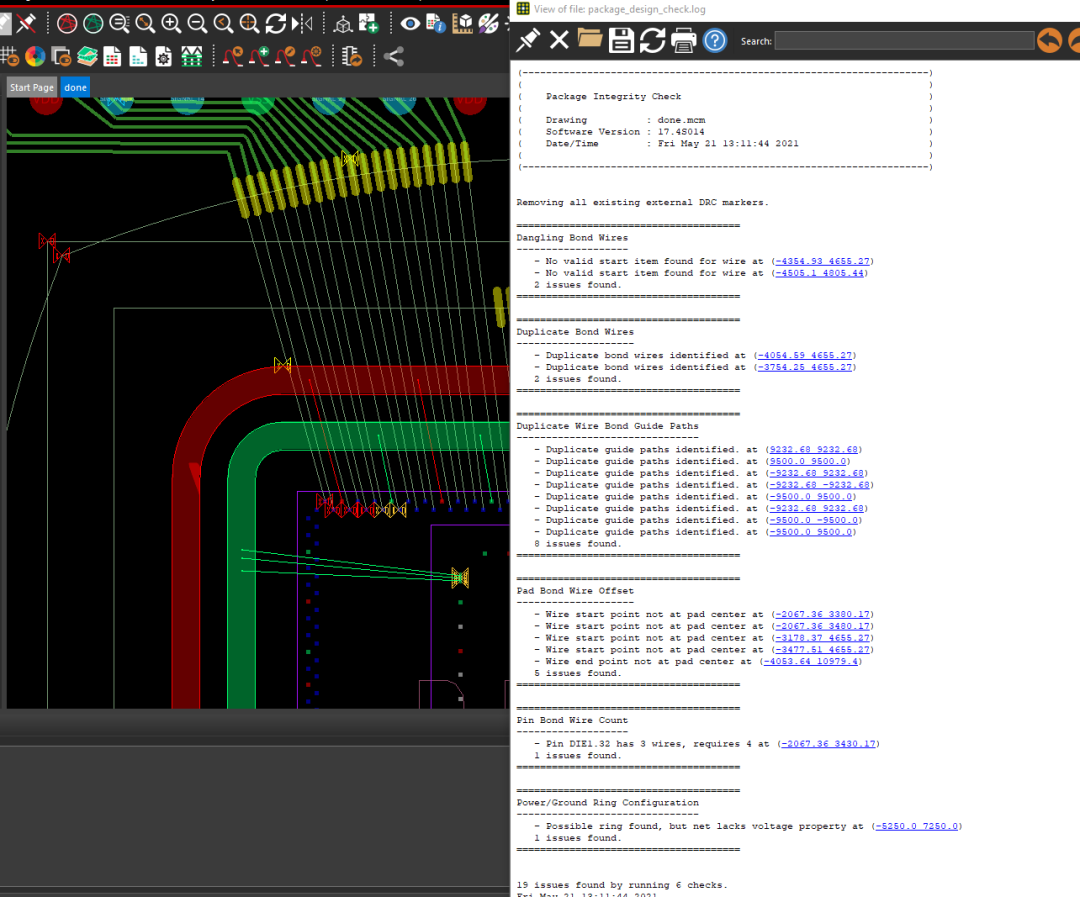

3. 打开日志文件,查看每个检查中的错误信息

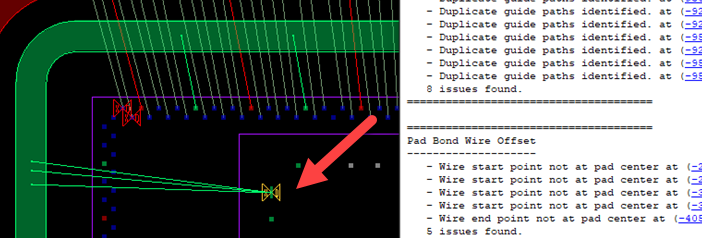

如图所示,会突出显示许多针对引线键合封装设计的完整性检查。每个实例上都有一个 DRC 标记。如果在设计画布中没有看到 DRC 标记,请确认 DRC 在 Visibility 窗格中已启用。

修复与具体引线键合相关的封装设计完整性问题

1. 自动修复错误

这些问题有多种解决方法。下面的例子中使用了一些我们推荐的方法:

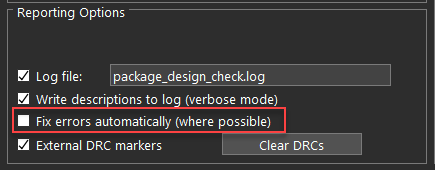

最好且最简单的方法之一是让应用程序自动修复错误。在 Package Design Integrity Checks 用户界面中,在 Reporting Options 部分启用 Fix errors automatically 选项(在可能的情况下),然后点击 OK,自动运行检查和修复错误。

通过该选项可以快速有效地清除大多数关于引线键合的设计问题。

接下来,让我们看看如何手动解决其中一些问题。

2. 修复引线的键合

在本例中,一些引线和相关的引脚位于不同的网络上。如果 die 有发生 ECO 和连通性变化,而这些变化没有通知到设计的其他部分,就会出现这种问题。要移除这些 DRC,请选择 Logic ─ Push Connectivity,将连通性从die的引脚传播到设计的其他部分。

3. 修复引脚连接线数量

本例有一个 VSS 引脚,需要连接到四根连接线,以达到低电感值。我们可以通过设置引脚上的 WIRE_COUNT 属性来指定连接线的数量要求。如下图所示,只有三根连接线连接到 VSS 引脚上,该引脚由指针标记。

必须在这个引脚上再连接一条连接线才能解决这个问题。要添加一条额外的连接线,请使用 Route ─ Wire Bond ─ Add 命令。

4. 修复电源/接地环的配置 本例中的另一个问题是没有为 VDD 网络分配正确的电压值。要修复这个错误,请使用 Logic ─ Identify DC Nets 命令,为 VDD 网设置电压值。

验证与具体引线键合相关的封装设计完整性问题

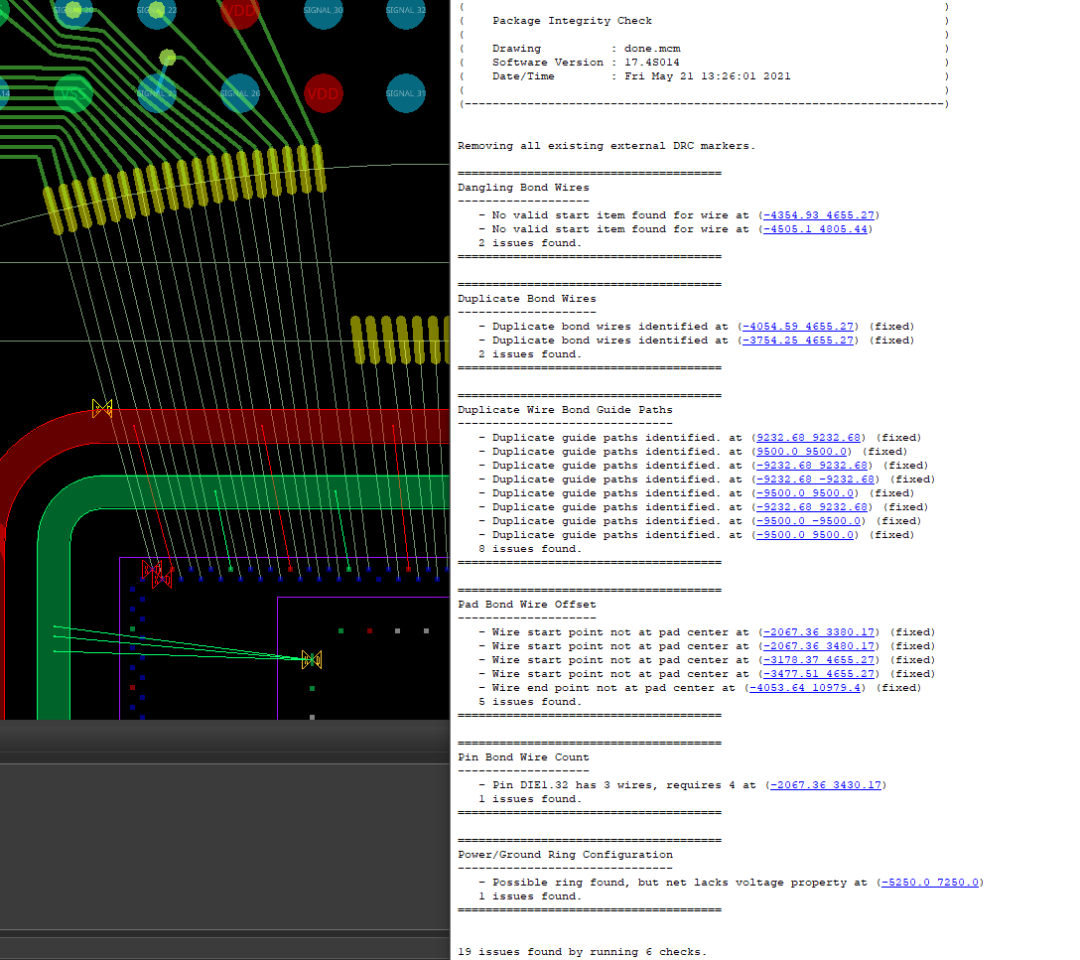

在修复所有的 DRC 后,再次运行封装设计完整性检查,以验证所有的问题都已解决。在运行检查之前,确保 Fix errors automatically 选项已被禁用。如下图所示,所有的 DRC 都已修复,并且在日志文件中没有报告任何问题。

Allegro Package Designer Plus 具有内置的自动化功能,能够分析和快速解决与具体引线键合相关的设计问题。运行封装完整性检查有助于设计师在前期修复大量的制造问题,如果到设计周期的后期阶段才发现这些问题,修复的代价将十分昂贵。

文章来源: Cadence楷登PCB及封装资源中心