高速信号目前已经成为PCB设计的主流,以通信产品为代表的电子类产品呈现高速化、高密化的技术发展趋势,给PCB设计工程师带来新的技术挑战。

高速信号PCB设计流程

当前的电子产品设计,需要更加关注高速信号的设计与实现,PCB设计是高速信号最终得以保证信号质量并实现系统功能的关键设计环节。

传统的PCB设计方式不关注PCB设计规则的前期仿真分析与制定,从原理图到PCB的设计实现没有高速信号规则约束,这样的传统设计方式在当前的高速信号产品研发体系中已经不可行,造成的后果一般是多次无效投板加工、不断测试优化与返工设计,造成研发周期变长、研发成本居高不下。

目前的高速信号PCB设计流程为:

① 高速信号前仿真分析

根据硬件电路模块划分与结构初步布局,仿真评估关键高速信号质量是否过关,如果不过关则需要修改硬件模块架构甚至系统架构;仿真信号质量通过的情况下,给出电路板大体模块布局方案及高速信号拓扑结构与设计规则

② 电路板布局设计

③ 电路板布线设计

根据电路板实际布线的情况,如果与前仿真制定的设计规则有出入,则需要再次仿真分析高速信号质量是否满足要求,例如:电路板线路布线密度过高、实际设计的线宽比前仿真设计规则要小、可能造成高速信号线路损耗过大、接收端信号幅度不满足芯片输入要求而导致电路板功能无法实现。

工程师需掌握的高速信号知识

(1)信号完整性基础知识

主要包括:传输线基本理论、阻抗控制原理、反射/串扰控制设计方法

(2)电源完整性基础知识

主要包括:电源噪声基本理论、电路板滤波原理与设计方法

(3)PCB原材料基础知识

主要包括:电路板铜箔、板材的电气特性

(4)信号拓扑结构知识

主要包括:常见的总线类型及PCB设计拓扑结构

常见信号拓扑结构

(1)点对点拓扑 point-to-point scheduling

该拓扑结构简单,整个网络的阻抗特性容易控制,时序关系也容易控制,常见于高速双向传输信号线;常在源端加串行匹配电阻来防止源端的二次反射。

(2)菊花链结构 daisy-chain scheduling

如下图所示,菊花链结构也比较简单,阻抗也比较容易控制。菊花链的特征就是每个接收端最多只和2个另外的接收端/发送端项链,连接每个接收端的stub线需要较短。该结构的阻抗匹配常在终端做,用戴维南端接比较合适。

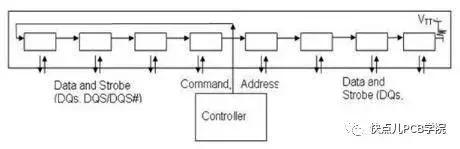

(3)fly-by scheduling

该结构是特殊的菊花链结构, stub线为0的菊花链。不同于DDR2的T型分支拓扑结构,DDR3采用了fly-by拓扑结构,以更高的速度提供更好的信号完整性。fly-by信号是命令、地址,控制和时钟信号。如下图所示,源于存储器控制器的这些信号以串行的方式连接到每个DRAM器件。通过减少分支的数量和分支的长度改进了信号完整性。然而,这引起了另一个问题,因为每一个存储器元件的延迟是不同的,取决于它处于时序的位置。通过按照DDR3规范的定义,采用读调整和写调整技术来补偿这种延迟的差异。fly-by拓扑结构在电源开启时校正存储器系统。这就要求在DDR3控制器中有额外的信息,允许校准工作在启动时自动完成。

在写调整期间,存储器控制器需要补偿额外的跨越时间偏移(对每个存储器器件,信号延迟是不同的),这是由于fly-by拓扑结构及选通和时钟引入的。源CK和DQS信号到达目的地有延迟。对于存储器模块的每个存储器元件,这种延迟是不同的,必须逐个芯片进行调整,如果芯片有多于一个字节的数据,甚至要根据字节来进行调整。该图说明了一个存储器元件。存储器控制器延迟了DQS,一次一步,直到检测到CK信号从0过渡到到1.这将再次对齐DQS和CK,以便DQ总线上的目标数据可以可靠地被捕获。由于这是由DDR3存储器控制器自动做的,PCB设计人员无须担心实施的细节。设计人员会从额外的裕度中得到好处,这是由DDR3存储器控制器中的写调整的特性所创建的。

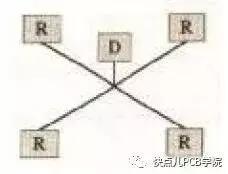

(4)星形结构 star scheduling

结构如上图所示,该结构布线比较复杂,阻抗不容易控制,但是由于星形堆成,所以时序比较容易控制。星形结构需要特别注意D点到适合于单项数据传输,从D-R,而不适合于从R-D。匹配方式一般在R端做匹配,消除终端反射。

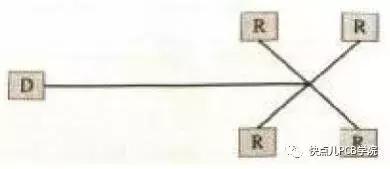

(5)远端簇结构 far-end cluster scheduling

远端簇结构可以算是星形结构的变种,要求是D到中心点的长度要远远长于各个R到中心连接点的长度。各个R到中心连接点的距离要尽量等长,匹配电阻放置在D附近,常用语DDR的地址、数据线的拓扑结构。

以上便是高速信号PCB设计知识。

文章转载自:快点PCB