高速PCB设计不断发展的今天,很多芯片的电源管脚都会使用滤波电容和旁路电源来进行滤波或者去耦,但是,每一个工程师在设计时摆放电容的方法或者方式不一样,可能会在去耦电容中形成大的电感,接下来我们将探讨与通孔和平面层配置相关的去耦电感问题并且怎么把去耦电感实现最小化。

针对高速去耦的领域,我们很多时候忽略了走线而比较喜欢用平面来连接。但是不管是走线连接还是用平面来连接,都会存在各种各样的问题,下面列出了我们常见的注意事项,让我们共同讨论这个话题。

1、高电感

经过实验验证得出使用过孔与平面层的连接相比,走线的连接方式会形成更多的电感的效应。

2、平面电容

随着工作频率的增加,去耦电容与平面相互作用的方式似乎成为主导因素。在某些情况下,去耦电容本身受到电感的阻碍,以至于它无法真正为IC提供电流。相反,平面电容提供的是瞬态去耦电流,这是电容器的工作状态是为平面充电。

3、紧凑的布局

复杂的高速数字系统通常在布局上显得很挤,因为这些空间主要是用来布局元器件。然而布局的越紧凑,相对来说走线空间就变得很小了,所以PCB Layout工程师会使用过孔来进行换层连接。

4、分布式电容与离散电容

如果平面电容是某些高速数字设计中去耦电荷的真正来源,那么电容真的需要“尽可能靠近引脚”吗?位置是否重要?通常大家都会质疑正确解耦的基本原则之一,但是这样的有效性结果显然会让令人震惊。但是在Hubing论文研究中有验证过。用这篇论文的作者的话来说。尽管他们可能已经将结论扩展到“研究的有效性范围之外,声称在某些条件下电容器的位置“不重要。无论如何,这是电容器之间相互作用重要性的一个例子。并且平面层在板上的任何地方都有“分布电容”的作用。

5、最小化电感

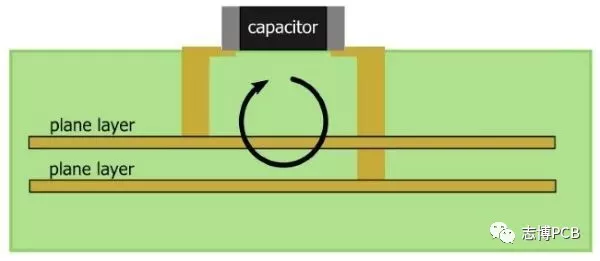

去耦电容器的总电感取决于由电容器,通孔和平面形成的电流回路的面积。

如您所见,环路区域受两个过孔之间的间隔以及电容器与平面层之间的距离的影响。因此,如果目标是改善去耦性能,则到平面的距离和通过分离是需要解决的关键因素。

6、到平面的距离

如果您正在设计一个典型的四层板,那么您可以做的就是减少与平面的距离 - 去耦帽将始终靠近一个平面层并且远离另一个平面层。

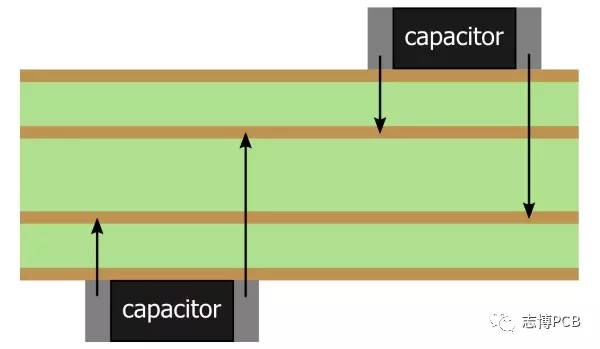

但是,如果电路板的层数超过四层,则可以灵活地优化去耦电容相对于电源和接地层的位置。此外,现在是指出如果不将电源和接地层放置在相邻层上,将会损失大量分布电容的好时机。在我看来,高速数字设计将从以下配置中受益匪浅:

在两个组件层之一上放置尽可能多的高速IC(让我们说它是顶部)。

布置电源和接地层,使它们相邻并靠近顶层。

将所有去耦帽放在顶层,使它们与平面有短连接。

7、通过分离

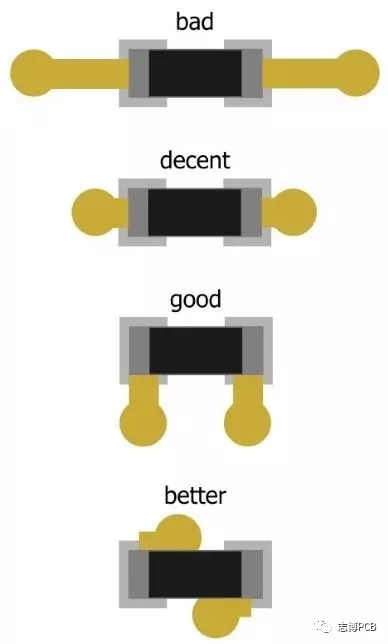

减少通孔分离的第一种方法是使用较小的去耦电容。在我的电路板上,我使用0603封装,因为我经常手工组装它们; 如果电路板将由机器组装,0402是更好的选择。

最小化电感现在是选择最佳通孔配置的问题:

请注意,我们主要关注两个过孔之间的距离。因此,第三个图标记为“良好”,第二个图标记为“正常”,尽管“体面”配置使用较短的迹线将电容器端子连接到通孔。

结论

我希望本文能让您深入了解高速数字PCB设计的复杂世界。我认为很明显,最小化环路面积是降低电感并因此提高高频性能的关键,但我不确定如何考虑在整个电路板上随机分配去耦电容的可能性(在某些情况下)。如果您对此主题有任何想法,请随时在评论中分享。

文章转载自:志博PCB