下面列举出四项很重要却常常被忽略的EMC设计指南。

设计指南1:最小化高频信号和电源环路面积

最小化高频信号和电源的环路面积几乎在所有的EMC设计指南中都有提到,但却常常被忽略。部分新手甚至不知道什么是信号回流路径。而信号回流路径是每位信号完整性和EMC工程师则必须思考的问题。下面是电路设计人员应该了解有关信号回流的两件事:

1.信号总是返回到源端(即信号电流路径总是环路的形式存在)

2.信号回流总是走阻抗最小的路径。

在上兆赫兹频率和更高频率时,信号回流路径相对容易找出来。这是因为高频下阻抗最小的路径通常是最小电感的路径,这通常也是环路面积最小的路径。信号回流尽可能靠近信号输出的路径返回。在低频的情况下(通常为KHz频率及以下),信号回流往往走阻值最小的路径。低频电流更难以追踪,因为在PCB内阻值最小路径较难寻找。低频情况下,信号回流路径有可能离信号走线较远。

设计指南2:不要拆分或切割信号回流平面,信号回流平面尽量完整

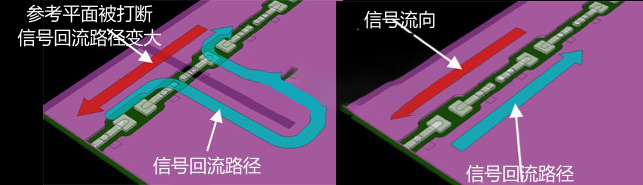

下图为没有提供良好的信号电流回路的情况,如回路接地平面有缝隙、布线参考平面换层等,则信号电流将不能经最优化(最短)路径返回源头,那么,信号电流将寻求替代的回流路径,此时将导致回流电流产生不可预期的路径,从而也增大信号环路面积。

特殊情况下,数字地和模拟地需要分隔,防止串扰。一般情况下,不要考虑拆分或切割电路板的信号回流平面。

设计准则3:高速电路不要走在连接器附近

为什么连接器的位置如此重要?在低于几百兆赫兹的频率下,波长大约为一米或更长。印刷电路板本身内部走线都很短,属于电小尺寸,因此辐射效率很低。然而,连接到板的电缆或其他设备则是高效的天线。

信号电流和回流路径导致回流平面上任意两点之间存在很小的电压差。这些电压差通常与平面内流动的电流的大小成正比。然而高速电路很容易产生几毫伏或更大的电位差。如果高速电路靠近连接器放置,这些电压会驱动电流到连接的电缆上,导致产品超过辐射发射要求。

设计指南4:抑制高速信号上升沿和下降沿时间

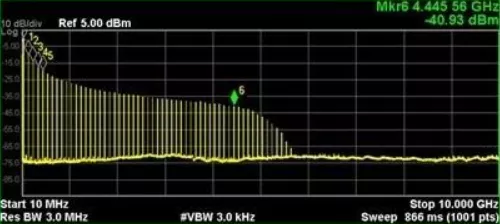

高速数字信号在较低谐波频率下具有大量能量,但在高次谐波中能量却不大,如下图时钟信号:

通过减慢数字信号的上升沿和下降沿时间,可以很好地控制高次谐波频率。过长的转换时间会导致信号完整性和过热问题,工程师需要在功能和EMC之间做折中考虑。

需注意的是,通过抑制信号回流来减慢或过滤单端信号高次谐波绝不是一个好主意。例如,不要将铁氧体串接在地上试图滤除高频噪声。

在PCB设计阶段做好上述4点设计指南,EMC测试和整改将会事半功倍。

文章转载自:韬略科技EMC