作者:蒋修国 信号完整性

编者注:本文内容看似简单,但是简单结果的背后却隐藏着很多深层次的问题,欢迎大家给出你们的答案。此类问题在多个行业产品当中常常会出现。

随着信号速率的提升,以及小型化产品的发展趋势,如何减小串扰变得越来越棘手。众所周知,串扰与很多因素有关系,比如传输线之间的间距,传输线耦合的长度,攻击信号的上升时间,阻抗不连续等等。因为串扰问题比较复杂,要是解决不好,还有可能会影响到其它信号完整性的问题。

今天给大家分享一个串扰引发损耗变大的问题。这类问题经常出现在小型化的产品、连接器、线缆等产品中。

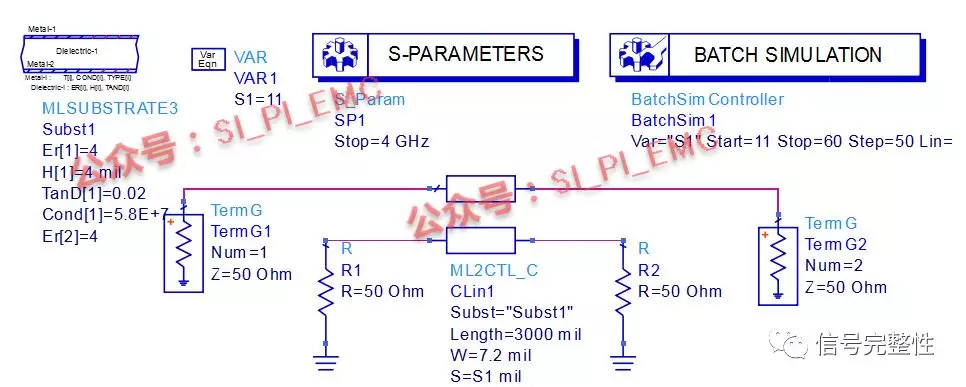

首先在ADS原理图中搭建一个仿真电路,扫描仿真间距为11mil和60mil两种情况。

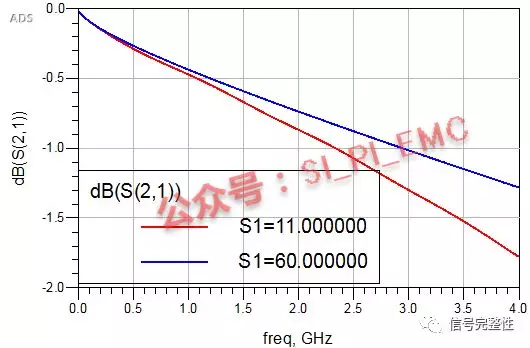

运行仿真之后查看插入损耗的结果:

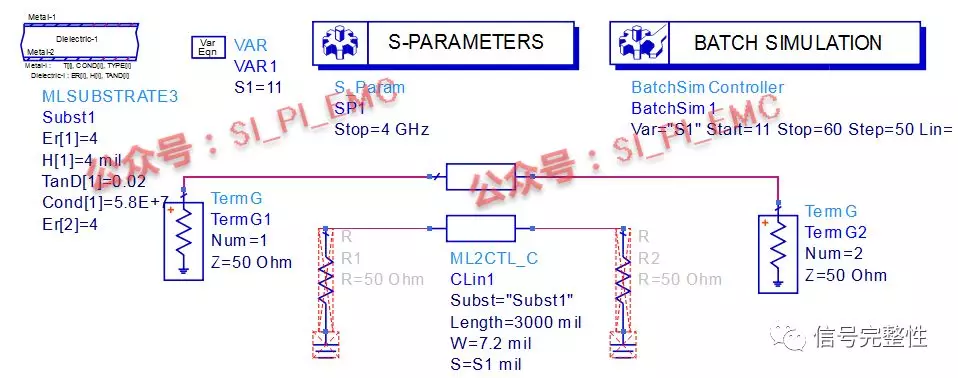

Disable电路图上的R1和R2:

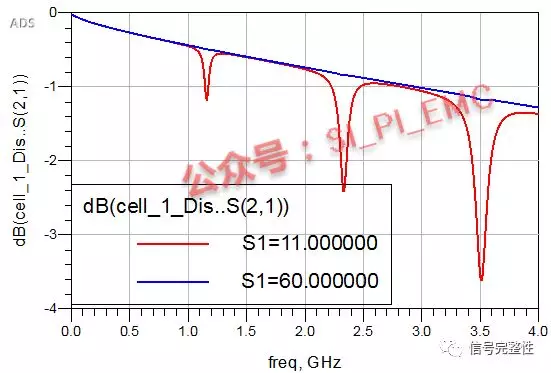

仿真如下图所示:

从结果上分析来看,去掉电阻后,距离为60mil时,结果几乎没有变化,但是间距为11mil时,结果却完全不一致,产生了三个非常大的谐振点。这就足以导致产品不满足设计的要求。

从上面仿真结果中,我们可以看到解决这个问题有两个非常便捷常用的方式,要么拉大距离、要么做好端接。大家可以相互讨论下有没有其它的解决方案呢?答案肯定是有的,大家可以多多讨论下。

免责声明:本文为网络转载文章,转载此文目的在于传播相关技术知识,版权归原作者所有,如涉及侵权,请联系小编删除(联系邮箱:service@eetrend.com )。