作者:蒋修国,文章来源:信号完整性微信公众号

编者注:在5G和高速数据传输的当前,设计和生产中往往会隐藏着很多问题小魔鬼,只有知其然,才能更好地找到解决之道。

不管是高速电路、高频电路还是毫米波,只要是电子产品基本都需要使用到PCB。PCB板的加工是一个非常复杂的系统工程,涉及到各个方面的问题,比如PCB材料、药水、加工工艺等等。在这个过程中会有很多因素对传输线的阻抗造成影响,比如PCB材料所涉及的铜箔厚度、介质厚度、介电常数、介质损耗角的影响,加工中涉及到的蚀刻因子(Etch),蚀刻药水的特性、加工稳定性等等。本文将从仿真的角度分析其中几个影响因子对阻抗的影响,当我们分析阻抗问题的时候可以多个思路。

1、传输线的线宽

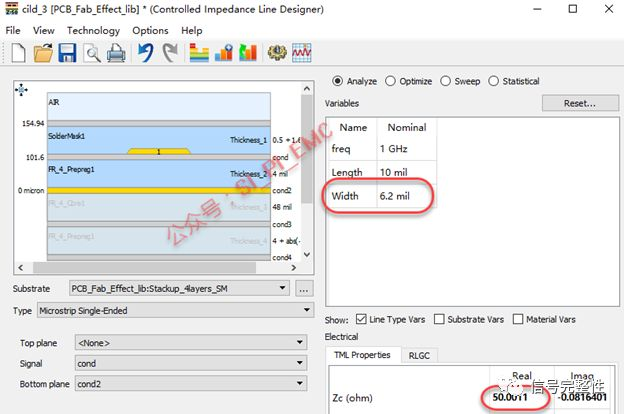

在以前的文章中介绍了很多关于线宽影响信号完整性的内容,我们知道线宽会直接影响到传输线的阻抗和损耗。大多数优秀工程师都会在给PCB生产商出Gerber时规定好线宽调整的范围,比如当线宽设计为6.2时,其阻抗为50ohm:

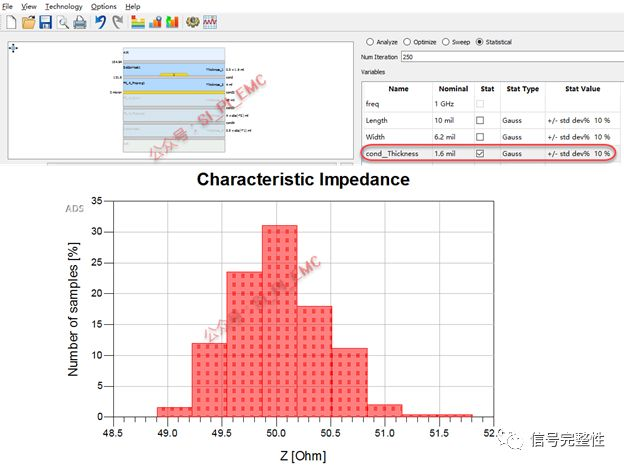

如果PCB在生产过程中工艺不稳定,导致线宽变化。依据与很多数厂商合作过的经验看来,传输线线宽的变化会在10%左右,所以把线宽变化的类型设置为Gauss分布,std设置为10%,进行统计学分析,在ADS CILD中仿真分析结果如下:

从结果上分析,阻抗最低会达到46ohm,而最高达到了58ohm;如果是在一段很长的传输线上,出现极端的状态是会存在的,那这时就会导致回波损耗比较大,同样插入损耗也有所增加。

2、铜箔/镀铜厚度

在PCB产品中,铜厚分为基铜厚度和镀铜厚度,基铜一般会比较均匀(这是相对的,其实也并不是完全均匀的),而镀铜的均匀性会随着工厂稳定性不同而不同,有的相差还比较大。镀铜厚度不同,同样会导致传输线阻抗和损耗的变化。把镀铜的变化范围假定为10%,在ADS CILD中进行统计分析,结果如下:

从结果分析来看,阻抗主要在49.5到51ohm之间变化。相对于线宽而言,变化区间会小不少。

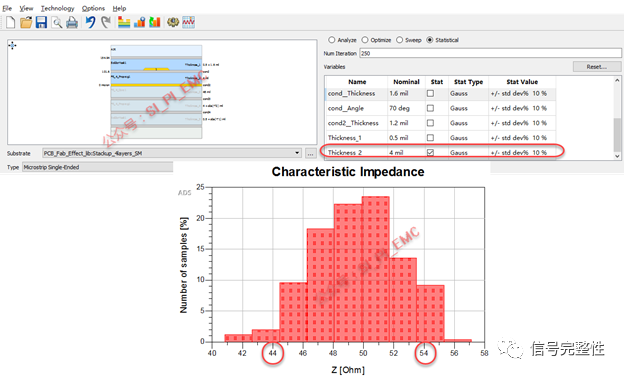

3、介质的厚度

在PCB生产中,介质厚度变化的主要来源是原材料和生产过程中的压合以及填胶。如果介质厚度变化,会造成阻抗的变化,以及损耗的变化,严重的情况会导致传输线很大的损耗。

从结果上分析,阻抗变化分布在44ohm到54ohm之间。阻抗变化的范围达到了10ohm之多。

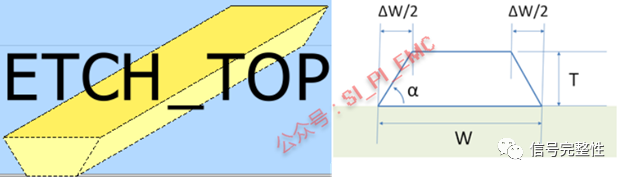

4、蚀刻因子

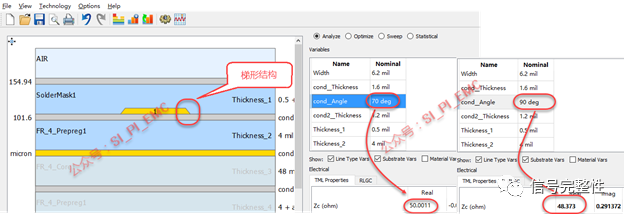

由于导体都是有一定厚度的,所以在生产中导致蚀刻出来的导线并不是一个标准的“矩形”结构,而是一个接近于“梯形”的结构(其实真实的状况也并不是完全的梯形结构),如下图所示为导体的一个示意图:

这个梯形的角度会随着铜厚的变化而变化(镀铜亦是如此),厚度越薄,角度越接近90°。这个角度的大小会影响到阻抗的大小。如下图所示为90°与70°结果的对比:

当角度为70°时,阻抗约为50ohm;当角度为90°时,阻抗约为48.37ohm。

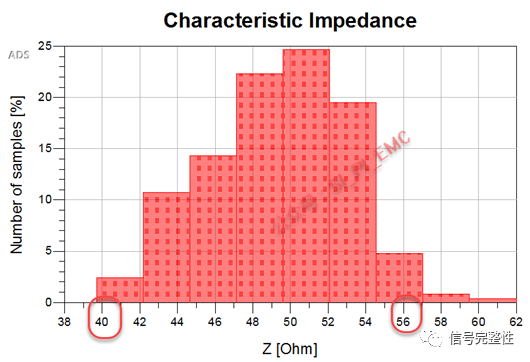

以上都是在单个因素变化下做的实验,而在生产过程中,并不是单一变量的变化,可能会同时发生。如果同时发生,那么其统计结果如下图所示:

从结果中可以看到阻抗主要在40ohm到56ohm之间变化,这个已经远远超过了一般50±10%的要求。而在整个生产过程中还不只是这些参数的变化会导致阻抗的变化。所以对于高速高频电路的产品,或者是高端产品,整个PCB设计和生产过程中都要严格控制好每一种物料以及每一个环节,否则就会导致产品出现一些意想不到的问题。